课程名称 课程工具 官网资源 软件安装 原理图设计 原理图实例 印制板图设计 器件的封装 PCB实例 实物展示(菲林、钢网)

信号完整性(Signal Integrity)

信号具有良好的完整性是指,当需要时 ,能够达到必须达到的电压电平数值。

由于深亚微米工艺在IC设计中的使用,芯片集成规模更大,高速时钟和高速器件开关,使得进行PCB设计和制造之前,对信号完整性分析变得越来越重要。(试错代价太高)

扩展:深亚微米集成电路:通常把0.35-0.8μm及其以下称为亚微米级,0.25um及其以下称为深亚微米,0.05um及其以下称为纳米级。深亚微米制造的关键技术主要包括紫外光刻技术、等离子体刻蚀技术、离子注入技术、铜互连技术(不是同互连)等。目前,国际上集成电路的主流生产工艺技术为0.010μm-0.028μm。

一般认为系统工作在50MHz时,就会产生信号完整性问题。随着频率的升高,信号完整性问题会越来越突出。

元器件、PCB参数、元器件在PCB上的布局、高速信号的布线等因素都和信号完整性有关。

在一个已有的PCB上查找信号完整性问题非常困难。所以在设计时做仿真是一项很值得的工作。

电路设计时,应注意以下几点:

1、对噪声敏感的元器件的物理隔离。

2、线路阻抗匹配及信号反射控制。

3、建议在设计中采用独立的电源及地电平层。

4、在PCB布线中信号线避免走直角。

5、同一组信号线尽量保持在布线上等长。

6、在高速电路设计中,相邻的两条信号线的间距应符合3W规则,及间距为信号线宽度的3倍。

7、对电源做好退耦处理,选择容值最够大的、低ESR的电容。

例子:Example\Reference Designs\4 port serial interface

1、【工具】\【信号完整性】

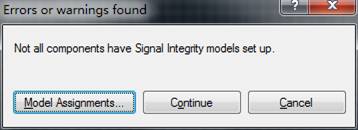

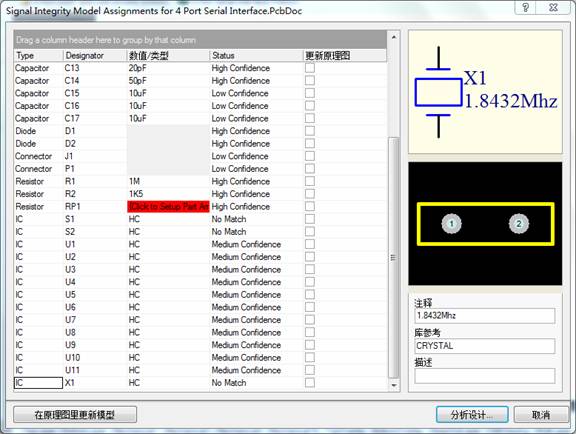

有的元件没有完整性模型,执行【Model Assignments】。

(状态说明,P328)

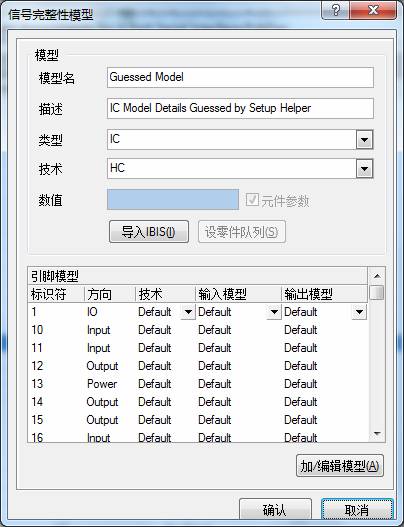

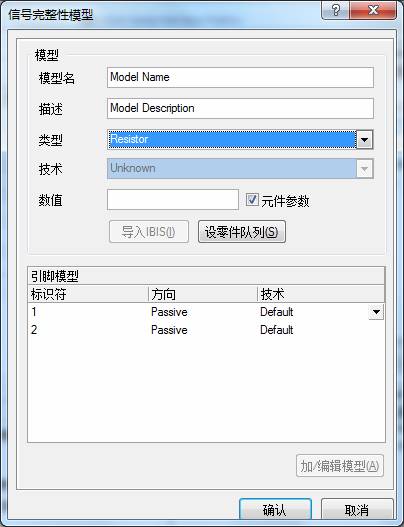

2、配置完整性模型

双击U1器件所在行,或者点击鼠标右键,选择【高级】。

选择合适的【类型】和【技术参数】。

单击【导入IBIS】,通过选择厂商提供的IBIS模型文件,加载模型。

IBIS:input/output buffer information specification,是基于V/I曲线对I/O buffer快速准确建模的方法,是一个国际标准。

设置完成后,执行【在原理图中更新模型】,将修改后的信号完整性分析模型保存到原理图中。

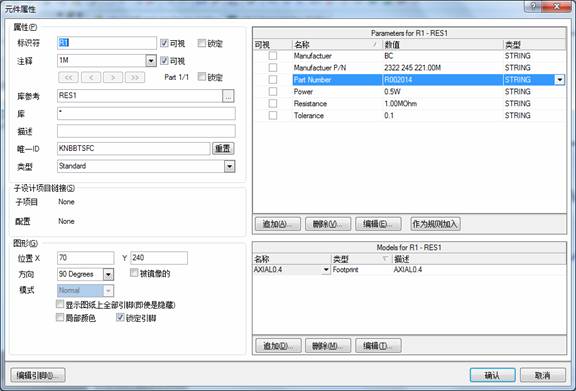

3、在元件属性中确定完整性模型。

Ctrl+f查找R1,单击鼠标右键查看元件属性。

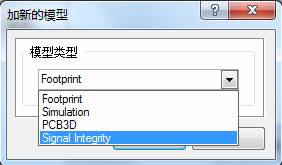

点击【追加】,在追加的模型类型中选择signal integrity。

又进入完整性模型设置窗口。

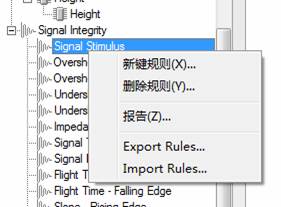

4、在PCB编辑状态下,执行【设计】/【规则】,查看【signal integrity】相关规则,在欲加的项上,点击鼠标右键,【新建规则】。