课程名称 课程工具 官网资源 软件安装 原理图设计 原理图实例 印制板图设计 器件的封装 PCB实例 实物展示(菲林、钢网)

|

http://www.mr-wu.cn/huawei-si-pi/ |

|

看看人家华为是如何进行信号完整性及电源完整性仿真分析的 |

|

信号与电源完整性

by xfire

华为公司互联设计部(早期的名称为CAD部)为了开发高速电路,随后为了解决电路电源稳定性问题,先后开展了信号完整性和电源完整性的分析、研究工作,取得了一定成绩,在一定程度上,解决了产品开发中所遇到的问题,现将情况简介如下:

1.

关于信号完整性在华为的历程

华为公司互联设计部从1997年开始就意识到高速电路是需要深入研发的一个领域。从此成立了专门的团队投入到信号完整性分析的研究上面来。当时首先

的切入点就是IBIS模型的测试建模和仿真对比(注解:IBIS(Input/Output

Buffer Information Specification)模型是一种基于V/I 曲线的对I/O BUFFER 快速准

确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,提供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入负载等参数,非常适合做振荡和串扰等高频效应的计算与仿真。)。以此开始了最初的仿真和测试并积累了经验。99年初,华为的信号完整性技术首先在某宽带交互产品上面获得 成功应用,解决了50Mbps的并行总线的过冲和串扰问题,并推出了第一块1.25Gbps的高速串行总线背板。2002年,互联设计部建设完成了国内第

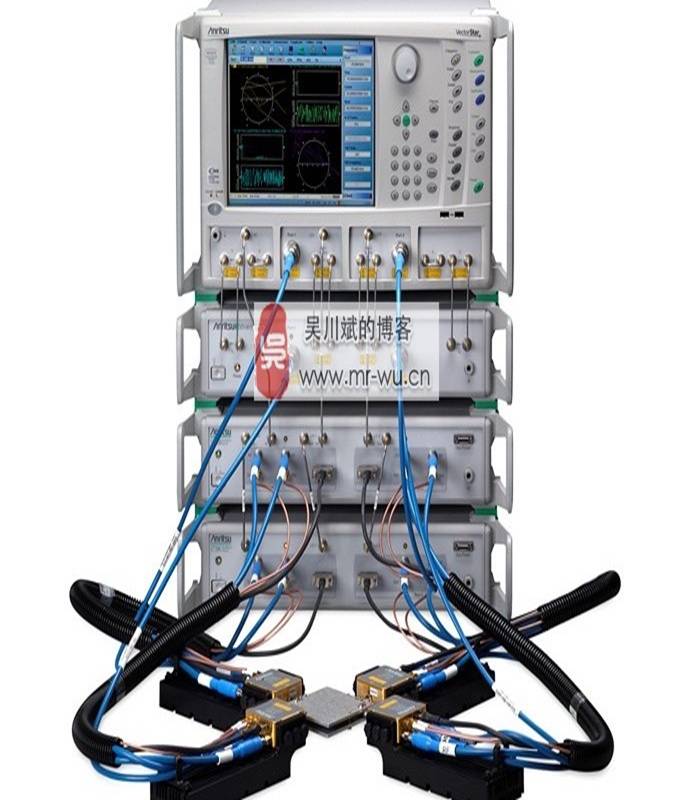

一个高速设计实验室,配置了完备的时域和频域测试和仿真环境,并在这个实验室里面,完成了3.125Gbps以上的高速背板研发工作。

2.

输入/输出缓冲信息规范模式(IBIS)数据库的建立 为了解决这个问题,华为设立了自己的模型小组作为EDA库管理的一部分。他们是元器件方面的专家,从供应商那里获得Spice模型后可以在其基础上 建立起行为级IBIS模型(注解:SPICE模型是由SPICE仿真器使用的基于文本描述的电路器件,它能够用数学预测不同情况下,元件的电气行为。SPICE模型从最简单的对电阻等无源元件只用一行的描述到使用数百行描述的极其复杂子电路。 SPICE模型不应该与pSPICE模型混淆在一起。pSPICE是由OrCAD提供的专用电路仿真器。尽管有些pSPICE模型是与SPICE兼容的,却并不能保证其完全兼容性。SPICE是最广泛使用的电路仿真器,同时还是一个开放式标准。)。如果是从供应商那里自己得到的IBIS模型,则对其准确性和语法进行检查。大约有20%的元件不能立即得到Spice或 IBIS模型,工程师们就直接从测量数据或产品规格中生成默认的模型,通常会将该模型与Spice模拟或测量的数据相比较,以确保其准确性。 |