Endianness

字节顺序

百度

字节顺序是指占内存多于一个字节类型的数据在内存中的存放顺序,通常有小端、大端两种字节顺序。小端字节序指低字节数据存放在内存低地址处,高字节数据存放在内存高地址处;大端字节序是高字节数据存放在低地址处,低字节数据存放在高地址处。

wikipedia

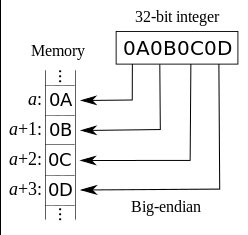

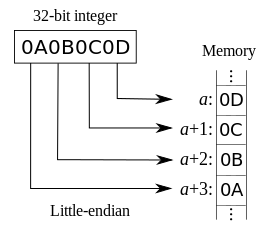

Endianness is the ordering or sequencing of bytes of a word of digital data in computer memory storage or during transmission. Words may be represented in big-endian or little-endian manner. Big-endian systems store the most-significant byte of a word at the smallest memory address and the least significant byte at the largest. A little-endian system, in contrast, stores the least-significant byte at the smallest address.

Big-endian

Atomic element size 8-bit

-

address increment 1-byte (octet)

| increasing addresses → | |||||

| 0Ah | 0Bh | 0Ch | 0Dh | ||

The most significant byte (MSB) value, which is 0Ah in our example, is stored at the memory location with the lowest address, the next byte value in significance, 0Bh, is stored at the following memory location and so on. This is akin to left-to-right reading in hexadecimal order.

Atomic element size 16-bit

| increasing addresses → | |||

| 0A0Bh | 0C0Dh | ||

The most significant atomic element stores now the value 0A0Bh, followed by 0C0Dh.

Little-endian

Atomic element size 8-bit

-

address increment 1-byte (octet)

| increasing addresses → | |||||

| 0Dh | 0Ch | 0Bh | 0Ah | ||

The least significant byte (LSB) value, 0Dh, is at the lowest address. The other bytes follow in increasing order of significance.

Atomic element size 16-bit

| increasing addresses → | |||||

| 0C0Dh | 0A0Bh | ||||

The least significant 16-bit unit stores the value 0C0Dh, immediately followed by 0A0Bh. Note that 0C0Dh and 0A0Bh represent integers, not bit layouts.

Middle-endian

Numerous other orderings, generically called middle-endian or mixed-endian, are possible. On the PDP-11 (16-bit little-endian) for example, the compiler stored 32-bit values with the 16-bit halves swapped from the expected little-endian order. This ordering is known as PDP-endian.

- storage of a 32-bit word (hexadecimal 0A0B0C0D) on a PDP-11

| increasing addresses → | |||||

| 0Bh | 0Ah | 0Dh | 0Ch | ||

The ARM architecture can also produce this format when writing a 32-bit word to an address 2 bytes from a 32-bit word alignment.

Segment descriptors on Intel 80386 and compatible processors keep a base 32-bit address of the segment stored in little-endian order, but in four nonconsecutive bytes, at relative positions 2, 3, 4 and 7 of the descriptor start.