参考文献:Nios II Processor Reference Handbook(page 48)

Nios II register (chinese)

The Nios II register set includes general-purpose registers and

control registers. In

addition, the Nios II/f core can optionally have shadow register sets.

This section

discusses each register type.

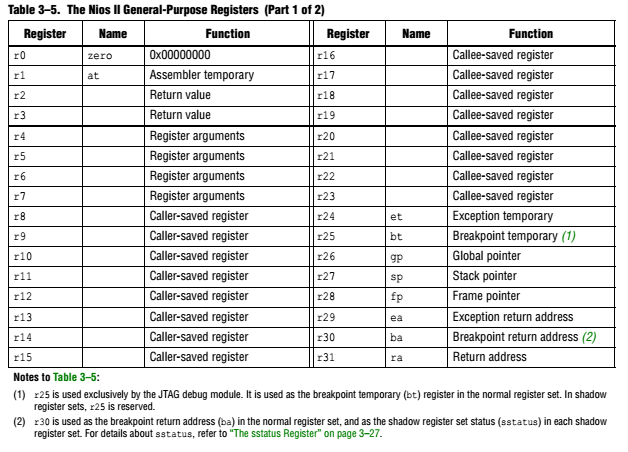

General-purpose Registers

The Nios II architecture provides thirty-two 32-bit general-purpose registers,

r0

through r31, as described in

Table 3–5. Some registers have names recognized by the

assembler. For example, the zero register (r0) always returns the value zero,

and

writing to zero has no effect. The ra register (r31) holds the return address

used by

procedure calls and is implicitly accessed by the call, callr and ret

instructions. C

and C++ compilers use a common procedure-call convention, assigning specific

meaning to registers r1 through r23 and r26 through r28.

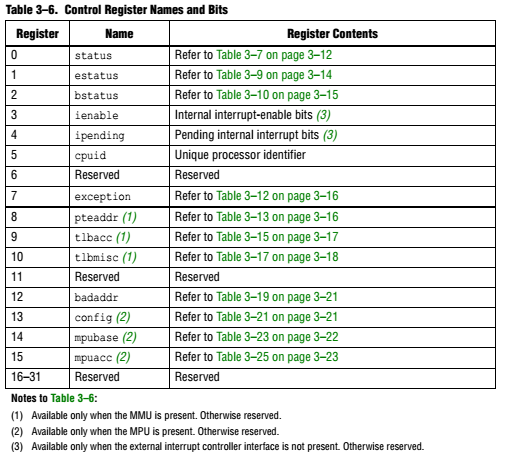

Control Registers

Control registers report the status and change the behavior of the

processor. Control

registers are accessed differently than the general-purpose registers. The

special

instructions rdctl and wrctl provide the only means to read and write to the

control

registers and are only available in supervisor mode.

When writing to control registers, all undefined bits must be written as zero.

The Nios II architecture supports up to 32 control registers. Table 3–6

lists details of

the defined control registers. All nonreserved control registers have names

recognized

by the assembler.

Shadow Register Sets

The Nios II processor can optionally have one or more shadow register sets. A

shadow register set is a complete alternate set of Nios II general-purpose

registers,

which can be used to maintain a separate runtime context for an interrupt

service

routine (ISR).

When shadow register sets are implemented,

status.CRS

indicates the register set

currently in use. A Nios II core can have up to 63 shadow register sets.

If n is the

configured number of shadow register sets, the shadow register sets are numbered

from 1 to n. Register set 0 is the normal register set.

A shadow register set behaves precisely the same as the normal register set. The

register set currently in use can only be determined by examining status.CRS.

Shadow register sets are typically used in conjunction with the EIC interface.

This

combination can substantially reduce interrupt latency.

For details of EIC interface usage, refer to “Exception Processing” on page

3–30.

System software can read from and write to any shadow register set by setting

status.PRS and using the rdprs and wrprs instructions.