Memory an I/O

(参考资料:Nios II processor reference handbook)

灵活

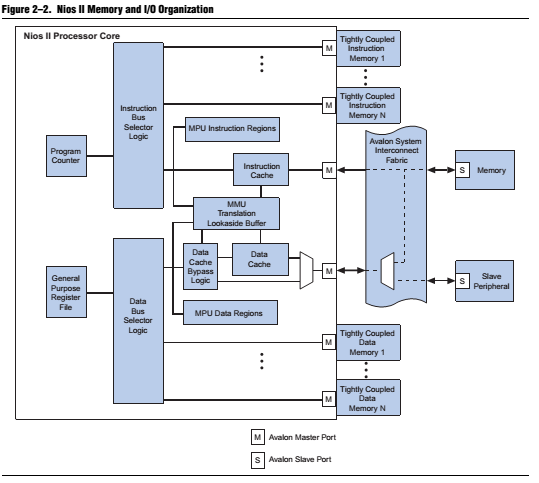

The flexible nature of the Nios II memory and I/O organization are the most notable difference between Nios II processor systems and traditional microcontrollers.Because Nios II processor systems are configurable, the memories and peripherals vary from system to system. As a result, the memory and I/O organization varies from system to system.

访问方式

A Nios II core uses one or more of the following to provide memory and I/O access:

■ Instruction master port—An Avalon® Memory-Mapped (Avalon-MM)

master port

that connects to instruction memory via system interconnect fabric

■ Instruction cache—Fast cache memory internal to the Nios II core

■ Data master port—An Avalon-MM master port that connects to data memory and

peripherals via system interconnect fabric

■ Data cache—Fast cache memory internal to the Nios II core

■ Tightly-coupled instruction or data memory port—Interface to fast on-chip

memory outside the Nios II core

The Nios II architecture handles the hardware details for the

programmer, so

programmers can develop Nios II applications without specific knowledge of the

hardware implementation.

Instruction and Data Buses 指令和数据总线

关键词:哈佛结构

The Nios II architecture supports separate instruction and data

buses, classifying it as a Harvard architecture. Both the instruction and

data buses are implemented as Avalon-MM master ports that adhere to the

Avalon-MM interface specification. The data master port connects to both memory

and peripheral components, while the

instruction master port connects only to memory components.

Memory and Peripheral Access 内存和外部设备的访问

关键词:统一地址空间

The Nios II architecture provides memory-mapped I/O access. Both data

memory

and peripherals are mapped into the address space of the data master port.

The

Nios II architecture uses little-endian byte ordering.

Words and halfwords are stored in memory with the more-significant bytes at

higher addresses.

The Nios II architecture does not specify anything about the

existence of memory and peripherals; the quantity, type, and connection of

memory and peripherals are

system-dependent. Typically, Nios II processor systems contain a mix of fast

on-chip memory and slower off-chip memory. Peripherals typically reside on-chip,

although interfaces to off-chip peripherals also exist.

Instruction Master Port

The Nios II instruction bus is implemented as a 32-bit Avalon-MM master port.

The

instruction master port performs a single function: it fetches instructions to

be

executed by the processor. The instruction master port does not perform any

write

operations.

Data Master Port

The Nios II data bus is implemented as a 32-bit Avalon-MM master port. The data

master port performs two functions:

■ Read data from memory or a peripheral when the processor executes a load

instruction

■ Write data to memory or a peripheral when the processor executes a store

instruction

Cache Memory

The Nios II architecture supports cache memories on both the instruction master

port(instruction cache) and the data master port (data cache). Cache memory

resides on-chip as an integral part of the Nios II processor core. The cache

memories can improve the average memory access time for Nios II processor

systems that use slow off-chip memory such as SDRAM for program and data

storage.

The instruction and data caches are enabled perpetually at run-time, but

methods are provided for software to bypass the data cache so that peripheral

accesses do not return cached data. Cache management and cache coherency are

handled by software.The Nios II instruction set provides instructions for cache

management.

例子:在实时采集图像数据时,要写入文件中,但是为了避免突然掉电带来的数据损失,需要将数据直接写到硬盘文件中。

Tightly-Coupled Memory

Tightly-coupled memory provides guaranteed low-latency memory access for

performance-critical applications. Compared to cache memory, tightly-coupled

memory provides the following benefits:

■ Performance similar to cache memory

■ Software can guarantee that performance-critical code or data is located in

tightly-coupled memory

■ No real-time caching overhead, such as loading, invalidating, or flushing

memory

Physically, a tightly-coupled memory port is a separate master port on the Nios

II

processor core, similar to the instruction or data master port. A Nios II core

can have zero, one, or multiple tightly-coupled memories. The Nios II

architecture supports tightly-coupled memory for both instruction and data

access. Each tightly-coupled memory port connects directly to exactly one memory

with guaranteed low, fixed latency. The memory is external to the Nios II core

and is located on chip.

Address Space and Memory Partitions

The MMU provides a 4-GB(why) virtual address space, and is

capable of addressing up to 4 GB of physical

memory.

The 4-GB virtual memory space is divided into partitions. The

upper 2 GB of memory is reserved for the

operating system and the lower 2 GB is reserved for user processes.