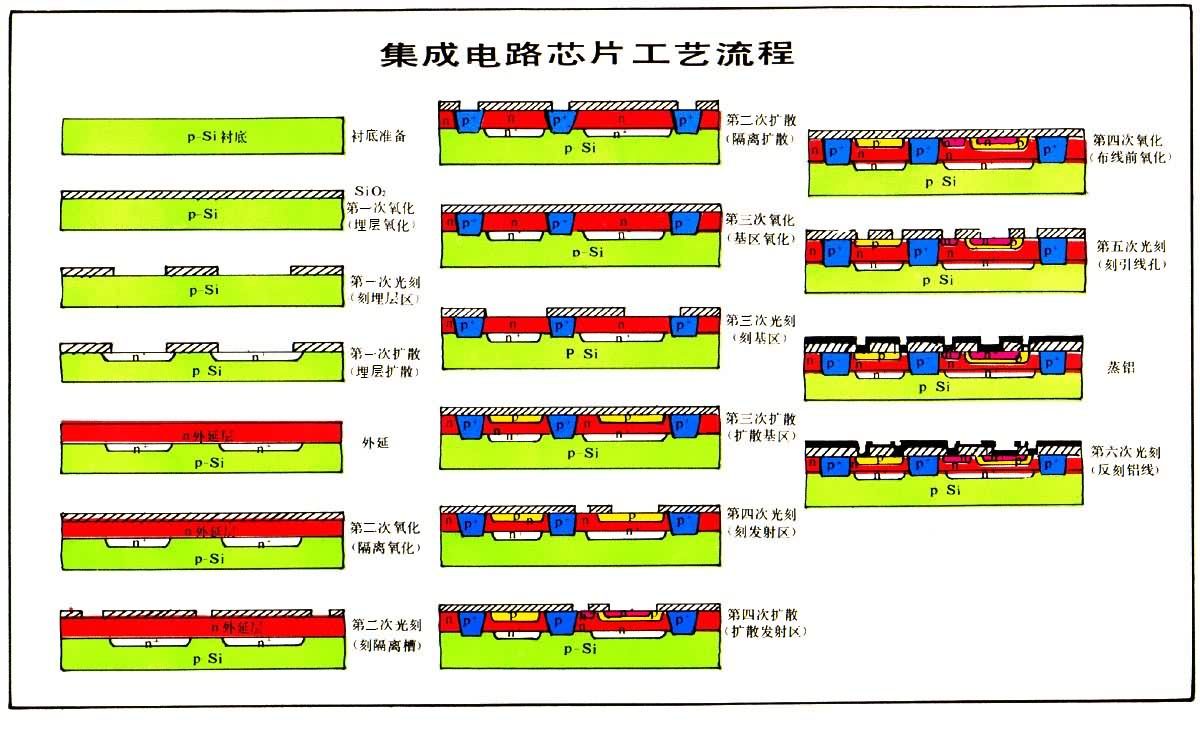

集成电路制造工艺流程

1.晶圆制造( 晶体生长-切片-边缘研磨-抛光-包裹-运输 )

晶体生长(Crystal Growth)

晶体生长需要高精度的自动化拉晶系统。

将石英矿石经由电弧炉提炼,盐酸氯化,并经蒸馏后,制成了高纯度的多晶硅,其纯度高达0.99999999999。

采用精炼石英矿而获得的多晶硅,加入少量的电活性“掺杂剂”,如砷、硼、磷或锑,一同放入位于高温炉中融解。

多晶硅块及掺杂剂融化以后,用一根长晶线缆作为籽晶,插入到融化的多晶硅中直至底部。

然后,旋转线缆并慢慢拉出,最后,再将其冷却结晶,就形成圆柱状的单晶硅晶棒,即硅棒。

此过程称为“长晶”。

硅棒一般长3英尺,直径有6英寸、8英寸、12英寸等不同尺寸。

硅晶棒再经过研磨、抛光和切片后,即成为制造集成电路的基本原料——晶圆。

切片(Slicing) /边缘研磨(Edge Grinding)/抛光(Surface Polishing)

切片是利用特殊的内圆刀片,将硅棒切成具有精确几何尺寸的薄晶圆。

然后,对晶圆表面和边缘进行抛光、研磨并清洗,将刚切割的晶圆的锐利边缘整成圆弧形,去除粗糙的划痕和杂质,就获得近乎完美的硅晶圆。

包裹(Wrapping)/运输(Shipping)

晶圆制造完成以后,还需要专业的设备对这些近乎完美的硅晶圆进行包裹和运输。

晶圆输送载体可为半导体制造商提供快速一致和可靠的晶圆取放,并提高生产力。

2.沉积

外延沉积 Epitaxial Deposition

在晶圆使用过程中,外延层是在半导体晶圆上沉积的第一层。

现代大多数外延生长沉积是在硅底层上利用低压化学气相沉积(LPCVD)方法生长硅薄膜。

外延层由超纯硅形成,是作为缓冲层阻止有害杂质进入硅衬底的。

过去一般是双极工艺需要使用外延层,CMOS技术不使用。

由于外延层可能会使有少量缺陷的晶圆能够被使用,所以今后可能会在300mm晶圆上更多采用。

9.晶圆检查Wafer Inspection (Particles)

在晶圆制造过程中很多步骤需要进行晶圆的污染微粒检查。

如裸晶圆检查、设备监控(利用工艺设备控制沉积到晶圆上的微粒尺寸),以及在CMP、CVD及离子注入之后的检查,通常这样的检查是在晶圆应用之前,或在一个涂光刻胶的层曝光之前,称之为无图形检查。

2.沉积

化学气相沉积 Chemical Vapor Deposition

化学气相沉积 (CVD) 是在晶圆表面通过分解气体分子沉积混合物的技术。

CVD会产生很多非等离子热中间物,一个共性的方面是这些中间物或先驱物都是气体。

有很多种CVD技术,如热CVD、等离子CVD、非等离子CVD、大气CVD、LPCVD、HDPCVD、LDPCVD、PECVD等,应用于半导体制造的不同方面。

3.光刻(Photolithography)

光刻是在晶圆上印制芯片电路图形的工艺,是集成电路制造的最关键步骤,在整个芯片的制造过程中约占据了整体制造成本的35%。

光刻也是决定了集成电路按照摩尔定律发展的一个重要原因,如果没有光刻技术的进步,集成电路就不可能从微米进入深亚微米再进入纳米时代。

光刻工艺将掩膜图形转移到晶片表面的光刻胶上,首先光刻胶处理设备把光刻胶旋涂到晶圆表面,再经过分步重复曝光和显影处理之后,在晶圆上形成需要的图形。

通常以一个制程所需要经过掩膜数量来表示这个制程的难易。

根据曝光方式不同,光刻可分为接触式、接近式和投影式;

根据光刻面数的不同,有单面对准光刻和双面对准光刻;

根据光刻胶类型不同,有薄胶光刻和厚胶光刻。

一般的光刻流程包括前处理、匀胶、前烘、对准曝光、显影、后烘,

可以根据实际情况调整流程中的操作。

4.刻蚀(Etching)

在集成电路制造过程中,经过掩模套准、曝光和显影,在抗蚀剂膜上复印出所需的图形,或者用电子束直接描绘在抗蚀剂膜上产生图形,

然后把此图形精确地转移到抗蚀剂下面的介质薄膜(如氧化硅、氮化硅、多晶硅)或金属薄膜上去,制造出所需的薄层图案。

刻蚀就是用化学的、物理的或同时使用化学和物理的方法,有选择地把没有被抗蚀剂掩蔽的那一部分薄膜层除去,从而在薄膜上得到和抗蚀剂膜上完全一致的图形。

等离子刻蚀(plasma etch)是在特定的条件下将反应气体电离形成等离子体,等离子体选择性地从晶圆上除去物质,剩下的物质在晶圆上形成芯片图形。

5.离子注入 Ion Implantation

晶圆衬底是纯硅材料,不导电或导电性极弱。

为了在芯片内具有导电性,必须在晶圆里掺入微量的不纯物质,通常是砷、硼、磷。

掺杂可以在扩散炉中进行,也可以采用离子注入实现。

一些先进的应用都是采用离子注入掺杂的。

离子注入有中电流离子注入、大电流/低能量离子注入、高能量离子注入三种,适于不同的应用需求。

6.热处理Thermal Processing

利用热能将物体内产生内应力的一些缺陷加以消除。

所施加的能量将增加晶格原子及缺陷在物体内的振动及扩散,使得原子的排列得以重整。

热处理是沉积制造工序后的一个工序,用来改变沉积薄膜的机械性能。

目前,热处理技术主要有两项应用:

一个使用超低k绝缘体来提升多孔薄膜的硬度,

另一个使用高强度氮化物来增加沉积薄膜的韧性抗张力,以提升器件性能。

在紫外热处理反应器里,等离子增强化学气相沉积薄膜经过光和热的联合作用改变了膜的性能。

高强度氮化薄膜中紫外热处理工艺使连接重排,空间接触更好,产生出了提高器件性能所需的高强度水平。

2.沉积(蒸发、溅射)

物理气相沉积 Physical Vapor Deposition

晶圆上最常见的金属互连材料是Al,通常应用物理气相沉积(PVD)法制备金属材料薄膜。

在PVD系统中用离子轰击Al靶,使靶材表面Al原子以一定能量逸出,然后在晶圆表面沉积。

PVD方法也用于沉积阻挡层和籽晶层,以及用于双嵌式互连的铜薄膜。

7.化学机械研磨 CMP

推动芯片技术向前发展的关键之一是每个芯片的层数在增加,一个芯片上堆叠的层数越来越多,而各层的平坦不均会增加光刻精细电路图像的困难。

CMP 系统是使用抛光垫和化学研磨剂选择性抛光沉积层使其平坦化。

CMP包括多晶硅金属介质(PMD) 平坦化、层间绝缘膜(ILD) 平坦化和钨平坦化。

CMP是铜镶嵌互连工艺中的关键技术。

8.晶圆检测 Wafer Metrology

在芯片制造过程中,为了保证晶圆按照预定的设计要求被加工必须进行大量的检测和量测,包括芯片上线宽度的测量、各层厚度的测量、各层表面形貌测量,以及各个层的一些电子性能的测量。

随着半导体工艺和制造技术的不断发展,这些检测已经成为提高量产和良率的不可缺少的部分。在铜互连工艺中,由于采用更精细的线宽技术和低k介电材料,需要开发更精密的测试设备和新的测试方法。

检测主要包括三类:光学检测、薄膜检测、关键尺寸扫描电子检测(CD-SEM)。晶圆检测的一个重要发展趋势是将多种测量方法融合于一个工艺设备中。

9.晶圆检查Wafer Inspection (Particles)

在晶圆制造过程中很多步骤需要进行晶圆的污染微粒检查。如裸晶圆检查、设备监控(利用工艺设备控制沉积到晶圆上的微粒尺寸),以及在CMP、CVD及离子注入之后的检查,通常这样的检查是在晶圆应用之前,或在一个涂光刻胶的层曝光之前,称之为无图形检查。

10.晶圆探针测试(Wafer Probe Test)

晶圆探针测试是对制造完成的晶圆上的每个芯片(Die)进行针测,测试时,晶圆被固定在真空吸力的卡盘上,并与很薄的探针电测器对准,细如毛发的探针与芯片的每一个焊接点相接触。在测试过程中,每一个芯片的电性能和电路机能都被检测到,不合格的晶粒会被标上记号,而后当芯片切割成独立的芯片颗粒时,标有记号的不合格芯片颗粒会被淘汰。

探针检测的相关数据,现在已经可以用来对晶圆制造中的良率提升提供帮助。

14.封装(Assembly & Packaging)

封装技术这几年发展非常快,这主要是因为(a)芯片的复杂程度越来越高:芯片中所含晶体管数量急剧增多,管脚也越来越多。需要新的封装技术满足这些需求。(b)电子产品小型化:现在的电子产品要求体积小,功能强大,功耗低,这也意味着对于丝焊要求更高,封装形式要适应这些变化。

晶圆上的芯片在这里被切割成单个芯片,然后进行封装,这样才能使芯片最终安放在PCB板上。这里需要用的设备包括晶圆切割机,粘片机(将芯片封装到引线框架中)、线焊机(负责将芯片和引线框架的连接,如金丝焊和铜丝焊)等。

在引线键合工艺中使用不同类型的引线:金(Au)、铝(Al)、铜(Cu),每一种材料都有其优点和缺点,通过不同的方法来键合。随着多层封装乃至3D封装的应用的出现,超薄晶圆的需求也在不断增强。

15.成品检测(Final Test)

因为最终的芯片良率不可能达到100%,芯片的检测就变得尤为重要。

如何检测出性能高的芯片,如何快速进行检测,考虑到每片芯片都要进行检测,晶圆厂就必须全盘平衡成本,这催生了检测功能更为强大、成本更为低廉、检测速度更快的新一代检测设备。